# Investigation of Comparator Topologies + and their Usage in a Technology - Independent Flash-ADC Testbed

Cand.-Ing. Öner B. Ergin

Prof. Dr.-Ing. Klaus Solbach

Department of Microwave and RF-Technology

University of Duisburg-Essen

Dipl.-Ing. Harald Bothe and Dipl.-Ing. Reimund Wittmann

Nokia Research Center Bochum

Prof. Dr.-Ing. Werner Schardein

University of Applied Sciences and Arts Dortmund

#### Contents

- Introduction

- State-of-the-Art Analog-to-Digital Converters (ADCs)

- Flash ADC

- Comparators

- Comparator Selection Procedure

- •Flash ADC Testbed Verification in 65 nm Technology

- Conclusion

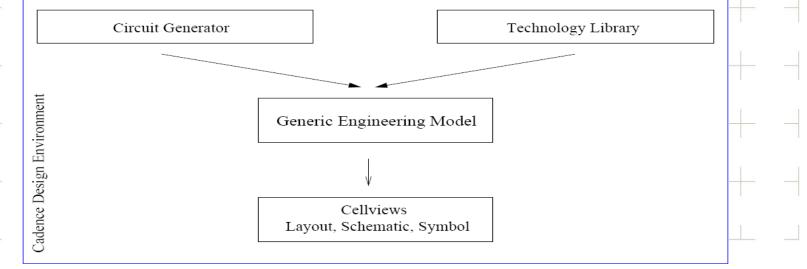

#### Introduction: Generic Engineering Model

- Variety of process technologies increases

- Circuits have to be rebuilt for every process

- •The Generic Engineering Model (GEM)

- Circuits are portable to all technologies

- Automatical symbol, schematic, layout and testbench generation

- •During this thesis, all circuits were developed using the GEM approach

#### Introduction: Selection methodology

- •Selection methodology on top of GEM implementation allows parameterizable layout solutions

- •Main high level design constraints:

- Power

- Supply voltage

- Area

- Bit resolution

- · Speed (clock rate)

- Comparator topologies are investigated with respect to the above listed constraints for flash ADC implementation

## Contents •State-of-the-Art Analog-to-Digital Converters (ADCs) Comparators Comparator Selection Procedure •Flash ADC Testbed Verification in 65 nm Technology •Conclusion + +

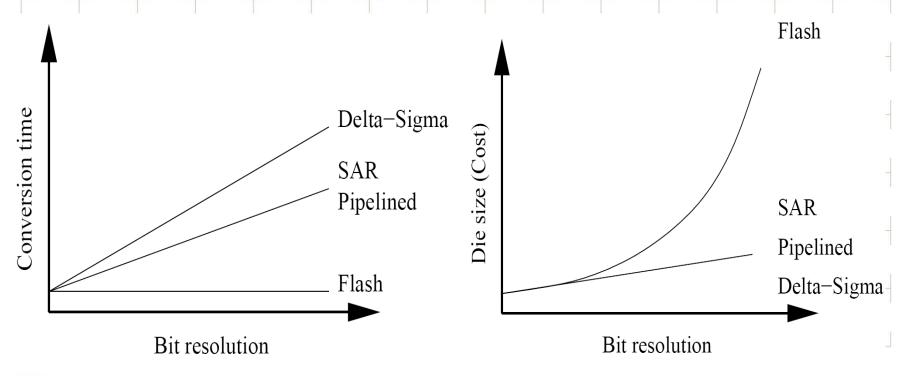

#### State-of-the-Art ADCs

- ADCs are developed for high speed or high resolution

- High resolution and high speed leads to high die size (high costs and implementation effort)

## Contents •State-of-the-Art Analog-to-Digital Converters (ADCs) •Flash ADC Comparators Comparator Selection Procedure •Flash ADC Testbed Verification in 65 nm Technology •Conclusion —

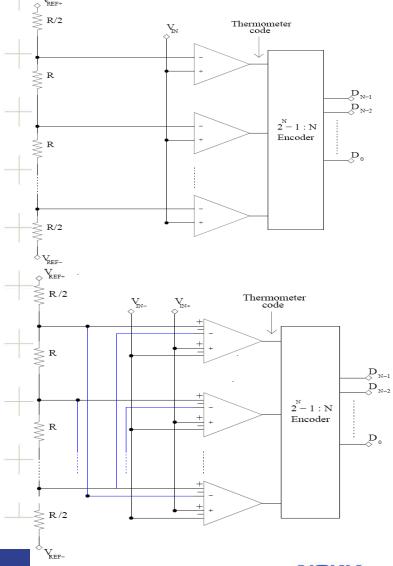

#### Flash ADC

- Fastest ADC structure

- •2<sup>N</sup> resistors , 2<sup>N</sup>-1 comparators, thermometer-code to binary encoder

- •Single-ended or differential type (wider intensity range)

- •Drawbacks (bit wise increase):

- Area and power double approximately

- Resistor matching becomes more critical

- Input bandwidth limited by increasing input capacitance

#### Contents State-of-the-Art Analog-to-Digital Converters (ADCs) Flash ADC Comparators **Comparator Specifications** Latch-Type Topologies SC-Type Topologies Simulation Results in 65 nm Technology Comparator Selection Procedure Flash ADC Testbed Verification in 65 nm Technology Conclusion

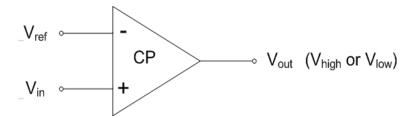

#### Comparators: Specifications

- Widely used components, especially in ADCs

- Comparator as 1-bit ADC

- Important specifications for implementation in flash ADCs:

- Bit resolution ( ≈ maximum bit resolution of flash ADC)

- Input common mode range (ICMR) ( ≈ maximum flash ADC approximation range)

- Speed (≈ maximum speed of flash ADC)

- Power ( ≈ minimum power dissipation of flash ADC (after division by the number of comparators))

- No Sample & Hold block needed when clocked comparators are implemented e.g.

- Latch-type comparatorsSC-type comparators

#### Contents State-of-the-Art Analog-to-Digital Converters (ADCs) Flash ADC Comparators **Comparator Specifications Latch-Type Topologies SC-Type Topologies** Simulation Results in 65 nm Technology Comparator Selection Procedure Testbed Verification in 65 nm Technology Conclusion

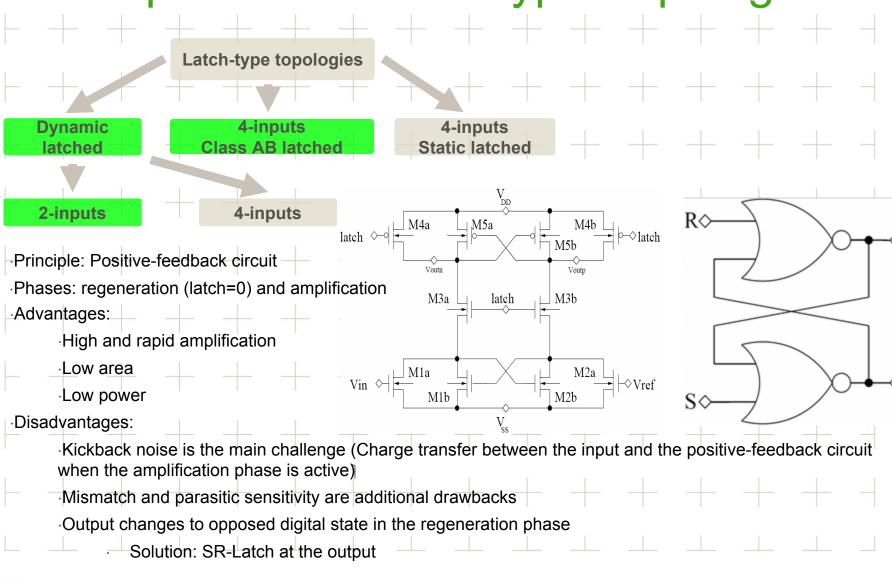

#### Comparators: Latch-Type Topologies

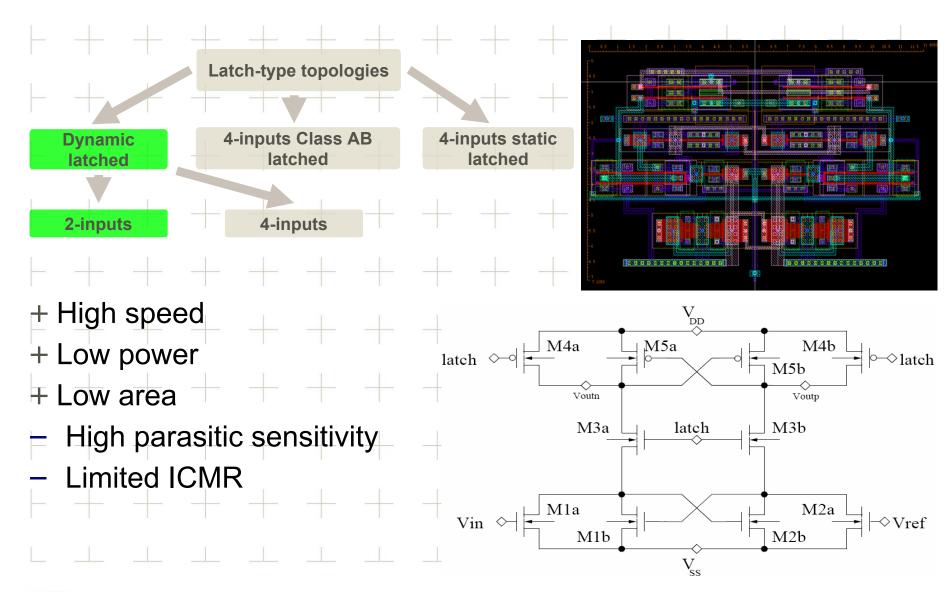

#### Comparators: Latch-Type: 2-inputs Dynamic Latched

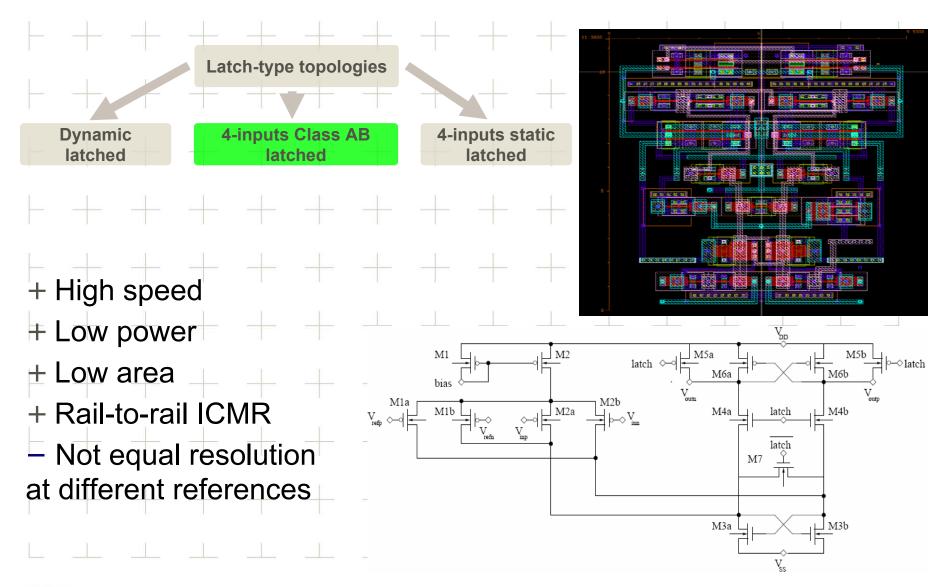

#### Comparators: Latch-Type: 4-inputs Class AB Latched

#### Contents •State-of-the-Art analog-to-digital converters (ADCs) Flash ADC Comparators **Comparator Specifications** Latch-Type Topologies **SC-Type Topologies** Simulation Results in 65 nm Technology Comparator Selection Procedure Testbed Verification in 65 nm Technology Conclusion

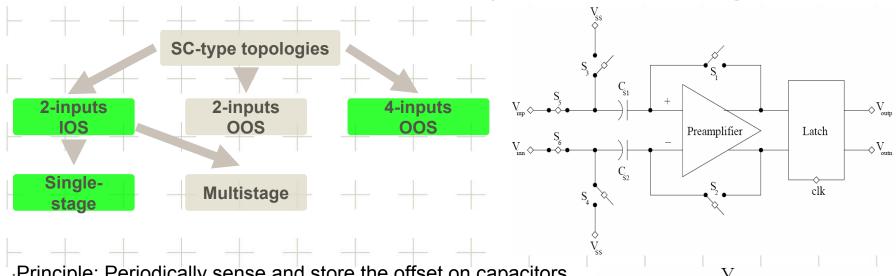

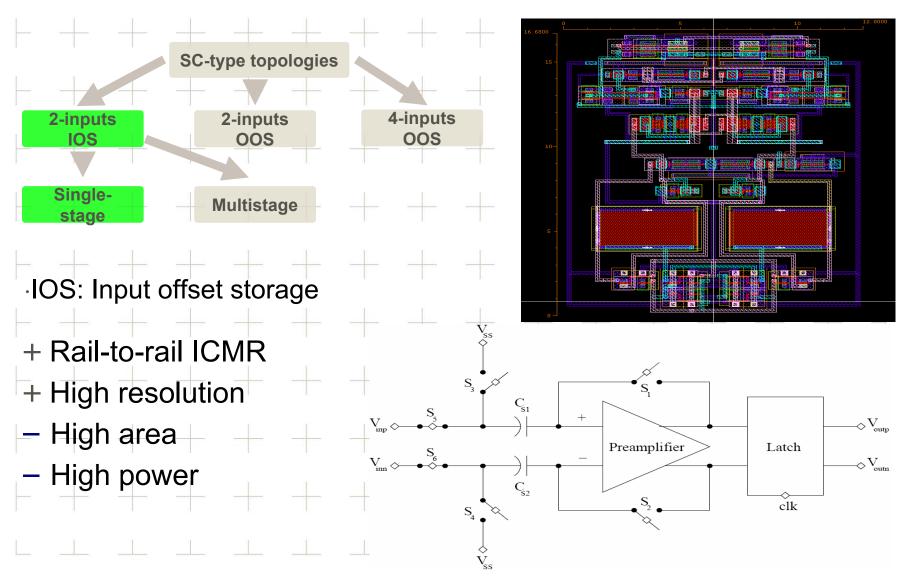

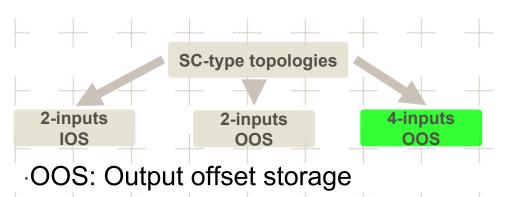

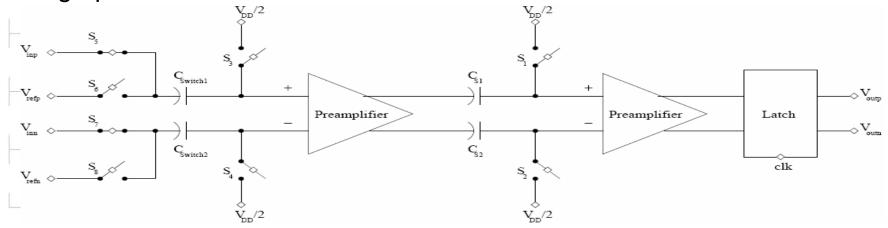

#### Comparators: SC-Type Topologies

- Principle: Periodically sense and store the offset on capacitors

- Phases: Offset cancellation, amplification and latch

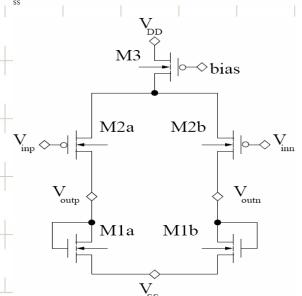

- A PMOS-input differential amplifier is used as the preamplifier

- The latch part is represented by the 2-inputs dynamic latched comparator

- Advantages

- High Resolution

- Disadvantages

- •High area

- High power

#### Comparators: SC-Type: 2-inputs IOS

#### Comparators: SC-Type: 4-inputs OOS

- + Rail-to-rail ICMR

- + High resolution

- High area

- High power

#### Contents State-of-the-Art Analog-to-Digital Converters (ADCs) Flash ADC Comparators **Comparator Specifications** Latch-Type Topologies **SC-Type Topologies** Simulation Results in 65 nm Technology Comparator Selection Procedure Flash ADC Testbed Verification in 65 nm Technology Conclusion

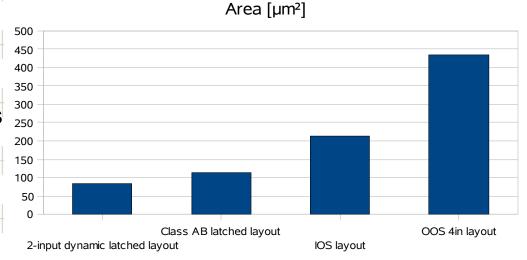

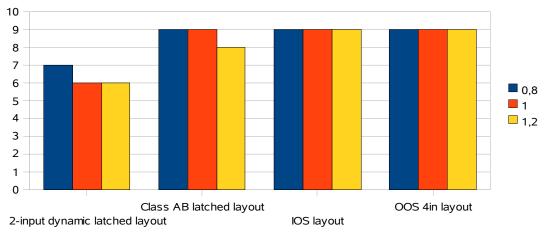

#### Comparators: Results: Area and Resolution

·Latch-type comparators

·Low area

Parasitic sensitivity degrades maximum resolution

SC-type comparators

·High area

·Less parasitic sensitivity

·Conclusion:

Lower area leads to less area consumption

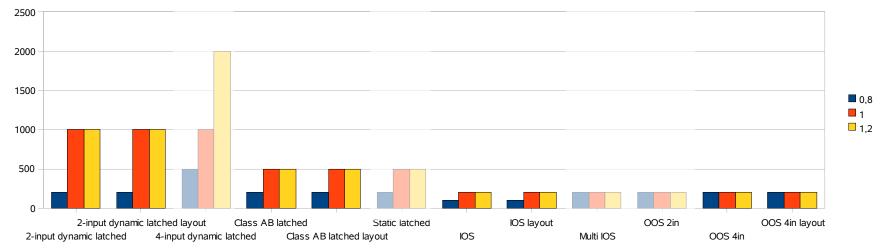

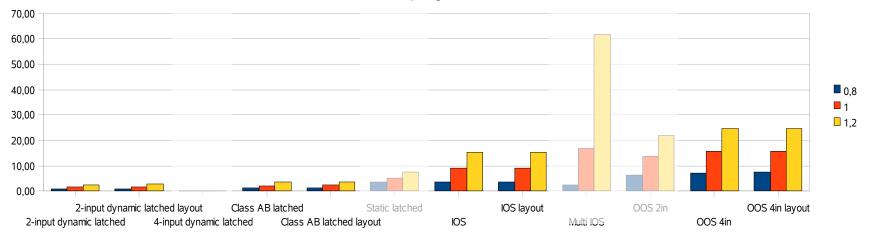

#### Comparators: Results: Speed and Power

#### Speed [MHz]

#### Power [µW] at 10 MHz

## Contents •State-of-the-Art Analog-to-Digital Converters (ADCs) Comparators Comparator Selection Procedure •Flash ADC Testbed Verification in 65 nm Technology •Conclusion — —

#### Comparator Selection Procedure

#### **Parameters**

Technology

Bit resolution

Speed

Approximation range

Supply voltage

2-inputs / 4-inputs

Comparator selection routine

#### Output

Relevant topologies Area consumptions Power dissipations

FAT tree encoder with single bubble error correction array GEM

**Comparator GEM**

Flash ADC testbed GEM

Poly resistor array GEM

UNIVERSITÄT DUISBURG ESSEN

### Contents •State-of-the-Art Analog-to-Digital Converters (ADCs) Comparators Comparator Selection Procedure •Flash ADC Testbed Verification in 65 nm Technology Layouts DNL/INL Results Conclusion

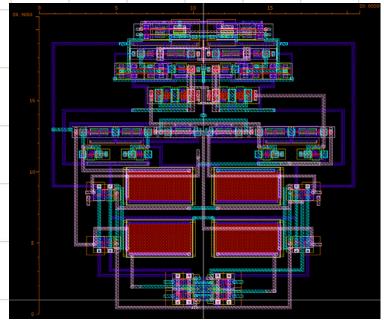

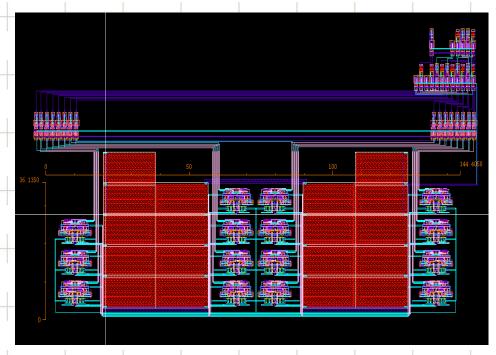

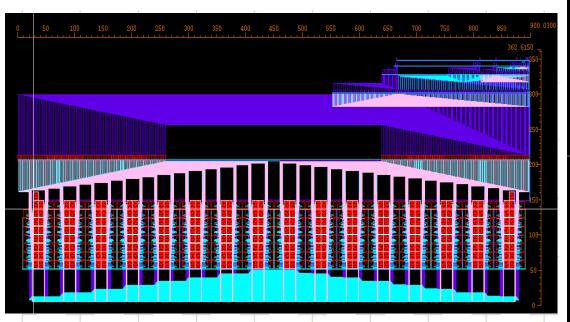

#### Flash ADC Testbed: Layouts: 4bit-flash ADC

- Checked and verified for resolutions

between 4 and 10 bit (DRC & LVS)

- Compatible for all analyzed comparators

- Dimension scalability:

(x-y distribution of comparators &

resistors is adjustable)

4bit Flash ADC layout; Implemented comparator: 2-inputs dynamic latched

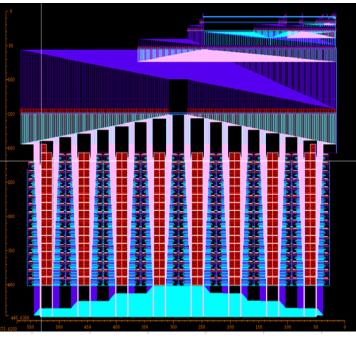

### Flash ADC Testbed: Layouts: Dimension Scalability with 8bit-Flash ADC

- Scalable X-Y distribution of resistors & comparators

- Left: 32 blocks with each 8 comparators & resistors

- Right: 16 blocks with each 16 comparators & resistors

- Implemented Comparator: 4-inputs Class AB latched

### Contents •State-of-the-Art Analog-to-Digital Converters (ADCs) Comparators Comparator Selection Procedure •Flash ADC Testbed Verification in 65 nm Technology Layouts DNL/INL Results Conclusion

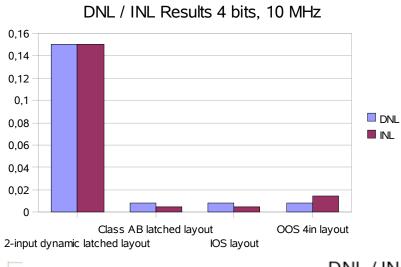

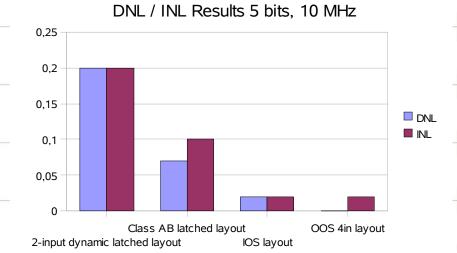

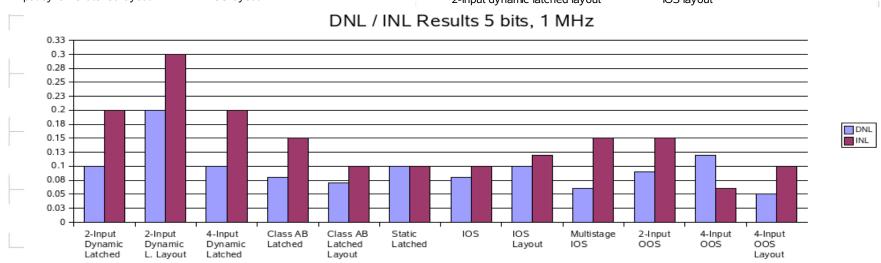

#### Flash ADC Testbed: DNL / INL Results

## Contents •State-of-the-Art Analog-to-Digital Converters (ADCs) Comparators Comparator Selection Procedure •Flash ADC Testbed Verification in 65 nm Technology •Conclusion

#### Conclusion

- Investigation of relevant comparator topologies:

- Latch-type comparators: + high speed, + low area, + low power, high parasitic sensitivity

- SC-type comparators: low speed, high area, high power, + low parasitic sensitivity

- Investigation and implementation of comparator selection procedure for the flash ADC testbed

- •A flash ADC GEM testbed has been developed, which is compatible to all analyzed comparators

- Checked and verified (DRC, LVS) for resolutions between 4 and 10 bits

- Integration of x-y dimension scalability

- Complex FAT tree encoder with single bubble error correction array implemented

- Functional verification (simulation of schematic and extracted layout view) has been done in 65 nm technology

- Selection methodology verified for all analyzed comparators

- •Main advantage of the selection methodology:

- Simplification of selection and implementation of flash ADCs referring to high-level demands

# Thank you for your attention!